14

Abstract

Digital signal processing (DSP) is an emerging technology that involves many disciplines and is widely used in many fields. Since the 1960s, with the rapid development of computers and information technology, DSP technology has emerged and developed rapidly. In the past two decades, digital signal processing has been widely applied in communication and other fields. DSP technology uses a computer or special processing equipment to collect, transform, filter, evaluate, enhance, compress, and identify digital signals in order to obtain a signal form that meets people's needs.

What is Digital Signal Processing Technology?

Catalog

I Basic Introduction of DSP Technology | |

II Implementation Method DSP Technology | 2.1 Implemented by Software |

2.2 Add a Dedicated Accelerated Processing Unit | |

2.3 Implemented by a Single-chip Microcomputer | |

2.4 Implemented with a Programmable DSP | |

2.5 Implemented with Dedicated DSP Chips | |

III History of DSP Technology | |

IV Difference between DSP and GPP Technology | 4.1 Support for Intensive multiplication operations |

4.2 Memory Structure | |

4.3 Zero-overhead Loop | |

4.4 Fixed-point Calculation | |

4.5 Prediction of Execution Time | |

4.6 Fixed-point DSP Instruction Set | |

4.7 Requirements for Development Tools | |

V Applications and Development DSP Technology | |

I Basic Introduction of DSP Technology

Digital signal processing is the technology that represents and processes signals in the form of digits, which belongs to signal processing like analog signal processing.

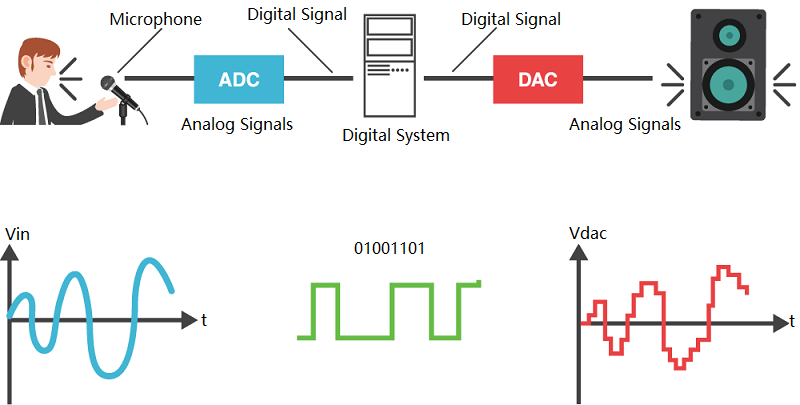

The purpose of DSP technology is to measure or filter continuous analog signals in the real world. Therefore, before performing digital signal processing, the signal needs to be converted from the analog domain to the digital domain, which is usually achieved by an analog-to-digital converter. And its output is often transformed into the analog domain by a digital-to-analog converter.

The algorithms of digital signal processing require the use of a computer or special processing equipment such as digital signal processors and application specific integrated circuits (ASICs). DSP technology and equipment have outstanding advantages such as flexibility, high precision, strong anti-interference performances, small size, low cost, and fast speed, which are unmatched by analog signal processing technology.

Digital signal processing is based on many disciplines, which covers a very wide range. For example, in the field of mathematics, calculus, probability statistics, stochastic processes, and numerical analysis are all basic tools for digital signal processing. It is also closely related to network theory, signals and systems, cybernetics, communication theory, and fault diagnosis. Besides, some recent emerging disciplines, such as artificial intelligence, pattern recognition, and neural networks, are also inseparable from digital signal processing. It can be said that DSP technology takes many classic theoretical systems as its theoretical foundation, and at the same time makes itself a theoretical foundation for a series of emerging disciplines.

II Implementation Method DSP Technology

The implementation methods of DSP are generally as follows:

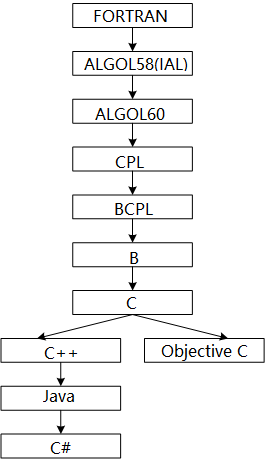

2.1 Implemented by Software (such as Fortran, C language) on a Common Computer (such as a PC)

The C++ Family Tree

2.2 Add a Dedicated Accelerated Processing Unit to the Computer System

2.3 Implemented by a general-purpose single-chip microcomputer (such as P8051, 96 series, etc.)

This method can be used for some less complex digital signal processing, such as digital control.

Intel P8051 Microcontroller

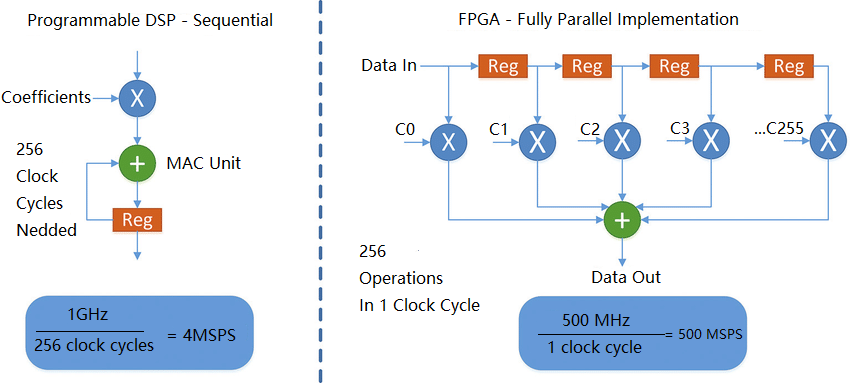

2.4 Implemented with a general-purpose programmable DSP

Compared with single-chip computers, DSP chips have more suitable software and hardware resources for digital signal processing, which can be used for complex digital signal processing algorithms.

Performance Comparison between Programmable DSP and New-dedicated DSP

2.5 Implemented with Dedicated DSP Chips

In some special occasions, the required signal processing speed is extremely high, which is difficult to achieve with general-purpose DSP chips. DSP chips dedicated to algorithms as FFT, digital filtering and convolution can internally integrate the corresponding signal processing algorithms with hardware without programming.

Among the methods above, the disadvantage of the first method is that it is slower and can generally be used for the simulation of DSP algorithms; the second and fifth methods have strong specificity, so their applications are greatly restricted, and the second method is not convenient for the independent operation of the system; the third method is only suitable for simple DSP algorithms; only the fourth method makes the application of DSP technology to a new situation.

III History of DSP Technology

The world's first single-chip DSP chip should be the S2811 released by AMI in 1978, and the commercial programmable device 2920 released by the American Intel Corporation in 1979 was a major milestone for DSP chips. Neither type of chip has the single-cycle multiplier necessary for modern DSP chips. In 1980, the μPD7720 launched by NEC of Japan was the first commercial DSP chip with a multiplier.

The Successor of μPD7720NEC— μPD96050

IV Difference between DSP and GPP

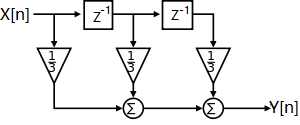

Let's take finite impulse response filter (FIR) as an example. In mathematical language, FIR filters do a series of dot products. It takes an input and an ordinal vector, multiplies the coefficients and the input samples between the sliding window, and then adds up all the products to form an output sample.

Similar calculations occur repeatedly in the digital signal processing process, which should be supported by designed devices to facilitate the shunting of DSP devices and general purpose processors (GPP).

Block Diagram of a Simple FIR Filter

4.1 Support for Intensive Multiplication Operations

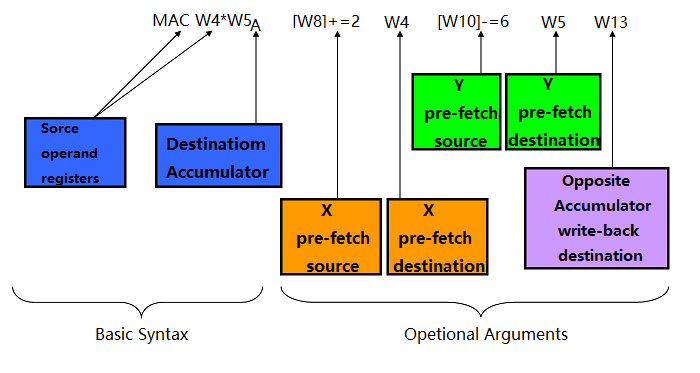

GPP is not designed to perform intensive multiplication tasks. Even some modern GPP require multiple instruction cycles to perform a multiplication, while the DSP processor uses specialized hardware to implement single-cycle multiplication. There is also an accumulator registers, which are usually wider than the other registers, to handle the sum of multiple products. At the same time, almost all DSP instruction sets contain explicit MAC instructions, which fully reflects the benefits of specialized multiply-accumulation hardware.

MAC Instruction Syntax

4.2 Memory Structure

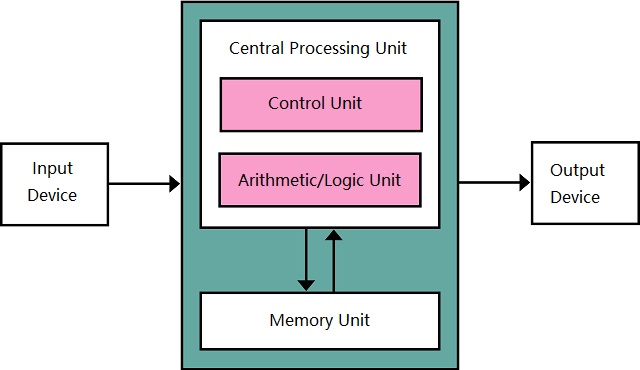

Traditionally, GPP uses the von Neumann memory structure. In this structure, only one memory space is connected to the processor core through a set of buses (an address bus and a data bus). Normally, doing a multiplication will result in 4 memory accesses, using at least four instruction cycles.

Von Neumann Structure Scheme

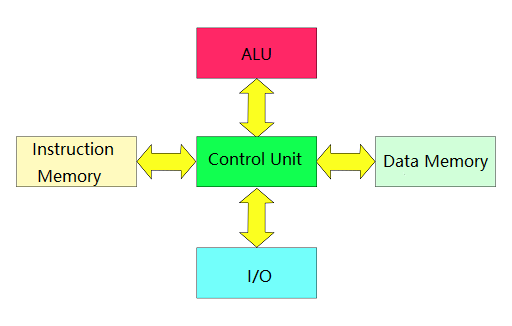

Most DSP use the Harvard structure, which has two memory spaces to respectively store programs and data. The two spaces have two sets of buses connected to the processor core, allowing simultaneous access to them. This arrangement doubles the bandwidth of the processor memory, and more importantly provides data and instructions to the processor core at the same time. In this layout, the DSP is able to implement a single-cycle MAC instruction.

Harvard Structure

Another problem is that the typical high-performance GPP now actually contains two on-chip caches, one for data and the other for instructions, which are directly connected to the processor core to speed up the access speed during the operation. Physically, the on-chip dual memory and bus structure is almost the same as the Harvard structure. However, logically, there are important differences between the two structures.

GPP uses control logic to decide which data and instruction words are stored in the on-chip cache, which the programmer does not specify (or may not know at all). In contrast, the DSP uses multiple on-chip memories and sets of buses to ensure multiple accesses to the memory in each instruction cycle. Besides, when using the DSP, the programmer must explicitly control which data and instructions to be stored in on-chip memory. And when programmers write programs, they must ensure that the processor can effectively use its dual bus.

Mutilple on-chip Memory

In addition, almost no DSP processor has a data cache for its typical data is a data stream. In other words, the DSP processor discards each data sample after calculation and almost never reuses it.

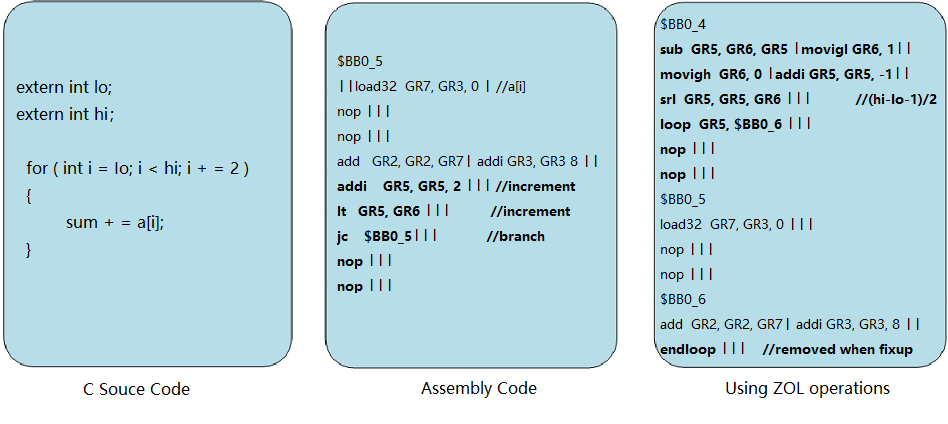

4.3 Zero-overhead Loop

If you understand a common feature of the DSP algorithms, that is, most of the processing time is spent executing smaller loops, it is easy to understand why most DSP have dedicated hardware for zero-overhead loops. The so-called zero-overhead loop means that when the processor executes the loop, we don't need to check the value of the loop counter.

In contrast, GPP cycles are implemented by using software. And some high-performance GPP use transition prediction hardware, which achieves almost the same effect as the zero-overhead loop supported by the hardware.

Zero Overhead Loop Code Transformation

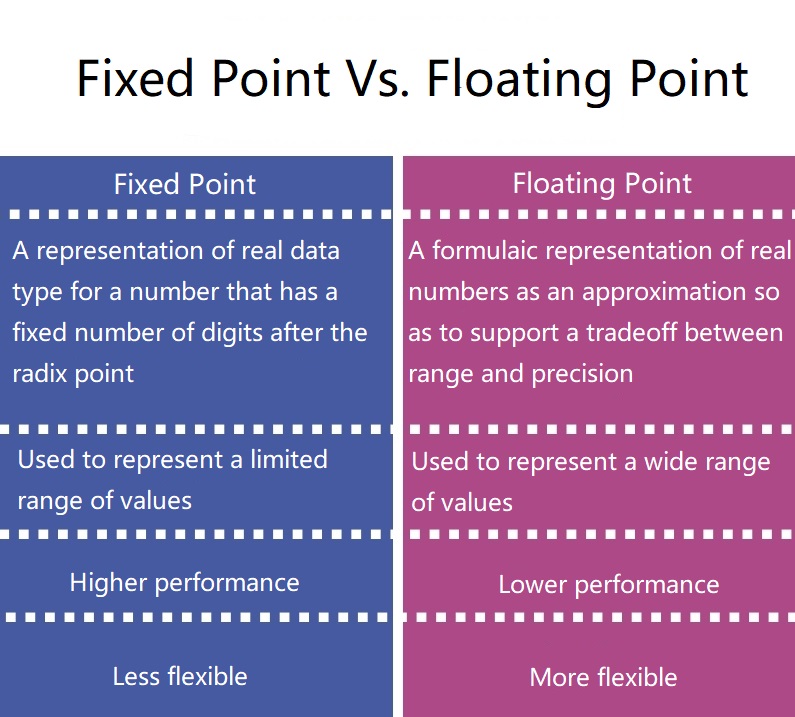

4.4 Fixed-point Calculation

Most DSP use fixed-point rather than floating-point for calculations. Although in the DSP application, we must pay great attention to the accuracy of the number, which is much easier to achieve by calculating with floating points. However, fixed-point machines are cheaper (and faster) than the corresponding floating-point machines. In order to not use floating-point machines and to ensure the accuracy of the numbers, the DSP processor supports saturated calculations, rounding, and shifting in both the instruction sets and hardware.

Specialized Addressing Mode

DSP processors often support specialized addressing modes, which are useful for general signal processing operations and algorithms. For example, module (cycle) addressing is useful for implementing delay lines of digital filters and bit-reversed addressing is useful for fast fourier transform(FFT). These specialized addressing modes are not commonly used in GPP for it uses software.

What is a Fast Fourier Transform (FFT)?

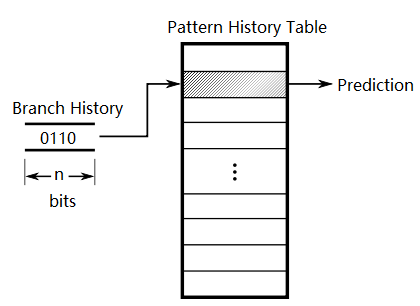

4.5 Prediction of Execution Time

Most DSP applications (such as cell phones and modems) are strictly real-time applications, whose processing must be completed within a specified time. This requires the programmers to exactly make sure how much processing time each sample needs, or at least know how much time it would take in the worst case.

If you plan to use low-cost GPP to complete the task of real-time signal processing, the prediction of execution time will probably not be a problem. Because the structure of low-cost GPP is relatively straight and direct, it is easier to predict the execution time. However, the processing capacity required by most real-time DSP applications cannot be provided by low-cost GPP.

Whereas if a cached DSP is used, as which instructions are put in are determined by the programmer (not the processor), it is easy to determine whether the instructions are read from the cache or the memory. DSP generally does not use dynamic characteristics, such as branch prediction and inference execution. Therefore, it's very easy to predict the required execution time from a given piece of code, which allows programmers to determine the performance limits of chips.

Two-level Adaptive Branch Predictor

4.6 Fixed-point DSP Instruction Set

The fixed-point DSP instruction set is designed with two goals:

(1) To enable the processor to complete multiple operations in each instruction cycle, thereby improving the computing efficiency of each instruction cycle.

(2) To minimize the memory space for storing DSP programs. This is particularly important in cost-sensitive DSP applications.

To achieve these goals, programmers of DSP processors are allowed to specify several parallel operations within a single instruction. For example, one instruction contains MAC operations, which means one or two data movements at the same time, and a single instruction contains all the operations required to calculate a FIR filter. The cost of this high efficiency is that its instruction set is neither visualized nor easy to use compared to the GPP instruction set.

GPP programmers usually don't care if the processor's instruction set is easy to use or not, because they generally use high-level languages such as C or C ++. While for DSP programmers, unfortunately, the main DSP applications are written in assembly language (at least partially optimized in assembly language). Why? There are two reasons for this.

(1) Most widely used high-level languages, such as C, are not suitable for describing typical DSP algorithms.

(2) The complexity of the DSP structure, such as multiple memory spaces and buses, irregular instruction sets, highly specialized hardware, etc., makes it difficult for compilers to write efficiently.

Even if the C source code is compiled into the assembly code of the DSP with a compiler, the optimization is still a heavy task. Typical DSP applications have a large number of calculation requirements and strict overhead restrictions, making the optimization of the program essential (at least to the most critical part of the program). Therefore, a key factor to consider when choosing a DSP is whether there are enough programmers who can better adapt to the DSP processor instruction set.

Difference Between Fixed Point and Floating Point

4.7 Requirements for Development Tools

Because DSP applications need highly optimized code, most DSP manufacturers will provide development tools to help programmers complete their optimization tasks. For example, most manufacturers provide simulation tools of processors to accurately simulate activities of processors during each instruction cycle. These are useful tools for ensuring real-time operation and code optimization.

GPP vendors usually do not provide such tools, mainly because GPP programmers do not usually need know the detail information of this level. GPP lacks simulation tools accurate to the instruction cycle, which is a big problem faced by DSP application developers. As it is almost impossible to predict the number of required cycles of a high-performance GPP for a given task, we cannot explain how to improve the performance of the code.

V Application and Development of DSP Technology

The demand for data communication in modern society is developing towards diversification and personalization. Under this conditions, 3G, 4G and even 5G communication are continuously launched. But no matter whether it is 4G or 5G, DSP technology will be indispensable in the future. As a powerful special microprocessor, DSP are mainly used in high-speed mathematical operations and real-time processing of data, voice, and video signals. It can be said that DSP will play an important role in the future communication field.

In order to ensure that future communications can work freely and efficiently in various environments, DSP must have high computing speeds for processing signals in order to achieve various complicated calculations, decompression, and coding.

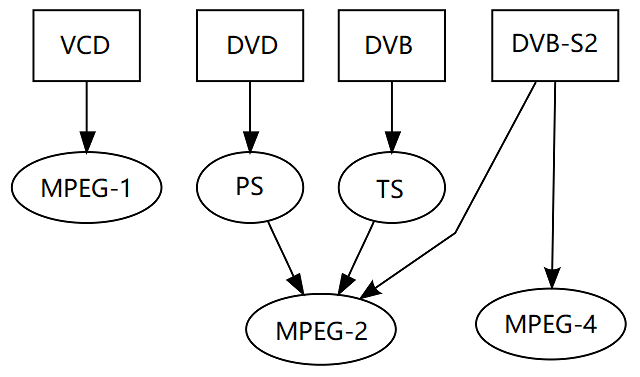

At present, according to the function of the DSP, there are fixed-point DSP and floating-point DSP. Fixed-point DSP is known for its low cost, floating-point DSP is characterized by its fast speed. If only one type of DSP is used, the potential of future communications cannot be maximized. Therefore, in order to combine the advantages of fixed point and floating point, and break through the bottleneck of DSP technology, an advanced multiprocessing structure--VLIW structure-- is introduced, which can achieve a strong digital signal processing capability without increasing the clock speed.

In order to launch a series of more high-end new technology platforms, people began to pay attention to the development of DSP core technology. The core of DSP is equivalent to the CPU of a computer, so the quality of the core structure will directly affect the performance, power consumption and cost of the entire DSP chip.

Considering the need for wireless access to the Internet and multimedia services in the future, Sun Microsystems in the United States is now preparing to embed the company's flagship product, PersonalJava, into the DSP in order to further improve the degree of automation and intelligence in signal processing. Of course, other software languages were also sneaked in the previous DSP, such as high-level C language, but this language was incapable of processing network resources and multimedia information. Whereas PersonalJava is a Java environment suitable for personal network connections and applications, based on which personal communication system can download data and images from the network and the Internet. In addition, people are still researching and developing a DSP that complies with the MPEG-4 wireless decompression standard. This compression standard will provide a basis for future communications and transmission of various multimedia information.

MPEG-4

You May Also Like:

What is Pulse Width Modulation(PWM)?

What Are the Essential Differences Between PLC and Microcontrollers?

Ordering & Quality

| Photo | Mfr. Part # | Company | Description | Package | Qty |

|

MKL15Z64VLK4 | Company:Freescale Semiconductor | Remark:IC MCU 32BIT 64KB FLASH 80LQFP | Package:80-LQFP |

MKL15Z64VLK4 Datasheet |

In Stock:664 Inquiry |

Inquiry |

|

MC33910G5AC | Company:NXP | Remark:IC SYSTEM BASIS CHIP 32LQFP | Package:32-LQFP |

MC33910G5AC Datasheet |

In Stock:5153 Inquiry |

Inquiry |

|

MBRD340G | Company:ON Semiconductor | Remark:DIODE SCHOTTKY 40V 3A DPAK | Package:TO-252-3, DPak (2 Leads + Tab), SC-63 |

MBRD340G Datasheet |

In Stock:604 Inquiry |

Inquiry |

|

MC9S08PT32VLC | Company:NXP | Remark:IC MCU 8BIT 32KB FLASH 32LQFP | Package:32-LQFP |

MC9S08PT32VLC Datasheet |

In Stock:103 Inquiry |

Inquiry |

|

DS1816-10+ | Company:Maxim Integrated | Remark:IC 2.88V O-D 10% TO92-3 | Package:TO-226-3, TO-92-3 (TO-226AA) |

DS1816-10+ Datasheet |

In Stock:156 Inquiry |

Inquiry |

|

MMA2204KEGR2 | Company:Freescale Semiconductor - NXP | Remark:ACCELEROMETER 112.5G ANAL 16SOIC | Package:16-SOIC (0.295", 7.50mm Width) |

MMA2204KEGR2 Datasheet |

In Stock:1330 Inquiry |

Inquiry |

|

MPC5123YVY400B | Company:NXP | Remark:IC MCU 32BIT 516FPBGA | Package:516-BBGA |

MPC5123YVY400B Datasheet |

In Stock:104 Inquiry |

Inquiry |

|

RCL1218100RFKEK | Company:Vishay | Remark:RES SMD 100 OHM 1W 1812 WIDE | Package:Wide 1812 (4532 Metric), 1218 |

RCL1218100RFKEK Datasheet |

In Stock:5040 Inquiry |

Inquiry |

|

MR27V1602ETN | Company:OKI | Remark: | Package:TSOP |

MR27V1602ETN Datasheet |

In Stock:721 Inquiry |

Inquiry |

|

73M2R010F | Company:CTS Electronic Components | Remark:RES SMD 0.01 OHM 1% 2W 2512 | Package:2512 J-Lead |

73M2R010F Datasheet |

In Stock:1263 Inquiry |

Inquiry |